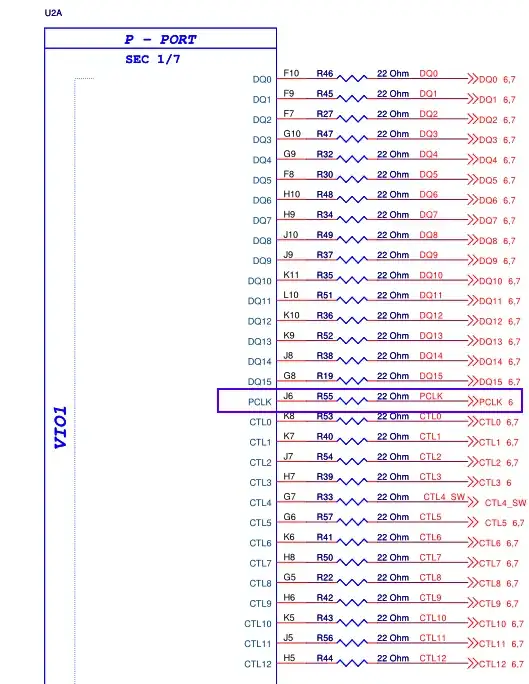

On a development board, I found this schematic for an up to 100 MHz clock input/output pin hooked up to a 2.54 mm pin header block:

The 22 ohm series termination makes sense if the pin is configured as an output, but how should this be driven as an input? I tested driving it from a ~20 ohm gate with no further termination through the header block (~3 cm of trace including header) and while everything works, there is a fair amount of over/undershoot visible on the scope due to reflections as compared to parallel terminated pins. What is the best practice in this situation?