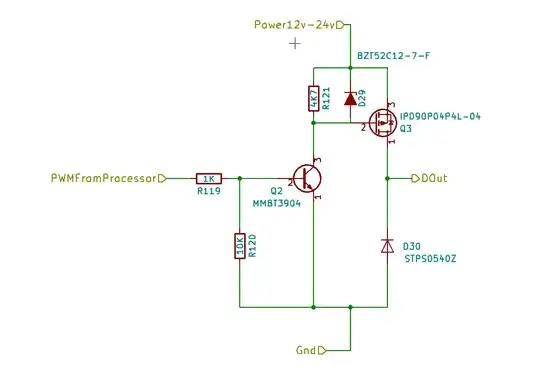

Here is your circuit:

All good now?

No. Think about what happens with 24 V supply. Q2 turns on, and the only load on the remaining nearly 24 V is a 12 V Zener. That's not going to end well. There is nothing limiting the current thru D29 and Q2.

A simple way to fix this with minimal change to your topology is to get rid of both R119 and R120, then add a resistor in series with the emitter of Q2. Q2 then becomes a switchable current sink.

The current must be enough to cause the required voltage drop across R121, plus some extra to reduce the switching time and make sure there is enough current thru the Zener for it to regulate its voltage. With 12 V across R121, it will draw 2.6 mA. Let's aim for about 5 mA sink current. With 3.3 V on the base of Q2, figure the emitter is at 2.6 V, so this indicates a emitter resistor of (2.6 V)/(5 mA) = 520 Ω. The common values of 510 Ω or even 560 Ω would work fine.

One drawback is that when the supply is only 12 V, the emitter resistor will eat up a vew volts and the gate will only be driven to about 9 V. Most FETs are still quite solidly on with 9 V on the gate, but check the datasheet.

However, overall I don't like this circuit for "PWM" because the gate is driven with relatively little current and the switching transition times will be long. A second BJT that clamps the gate voltage to the supply, but turns on for only a short time at the on-to-off transition would help. With a little cleverness, you can capacitively couple that from the high to low transition of the digital signal. But, the details of this are getting beyond the scope of this question.