Ideally a reference for small boards: The board that will be tested is 10 x 20 mm, and it's crowded. It doesn't have a lot of real estate left for test pads.

All I know is to look up IEEE papers:

Conformal surface lenses from a bed of nails https://ieeexplore.ieee.org/document/6901743

Bed of nails: fine pitch wafer-level packaging interconnects for high performance nano devices https://ieeexplore.ieee.org/document/1614483

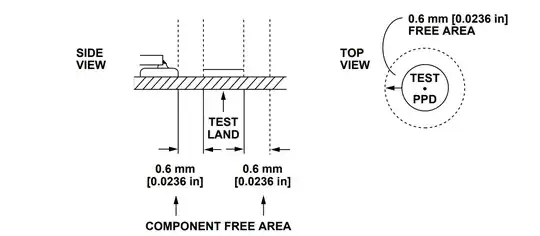

The best resource so far, was an article in Printed Circuit Design & Fab, which recommends 0.9 to 1.0 mm test pads.

For this specific case, six signals will be exposed to the bed-of-nails: power, ground and four digital signals This is to be able to change firmware after the board has been assembled. Two of the digital signals are not exposed on any connectors.