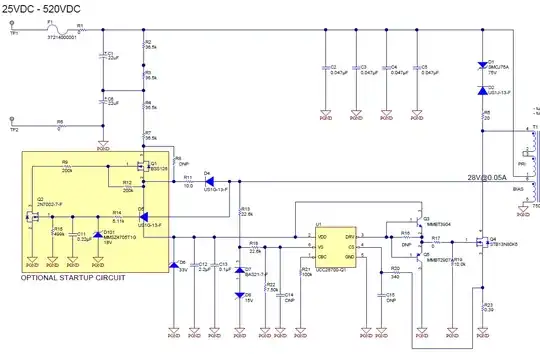

In the circuit below, how is Q1 turned on? When there's voltage in the bias winding, it turns Q2 On and subsequently turns Q1 off. Also, does the end of R4+R7 keep floating when Q1 is off? It should go to ground. I'd appreciate any help to better understand the startup circuit in the yellow square.

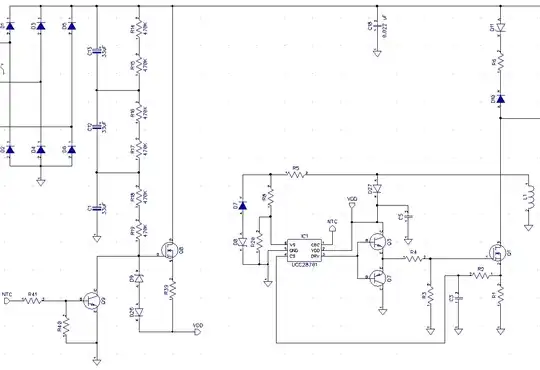

EDIT: Idea with an Enhancement MOSFET

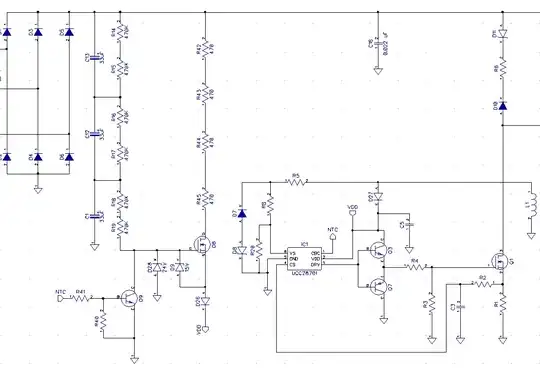

EDIT: Another approach with Enhancement MOSFET