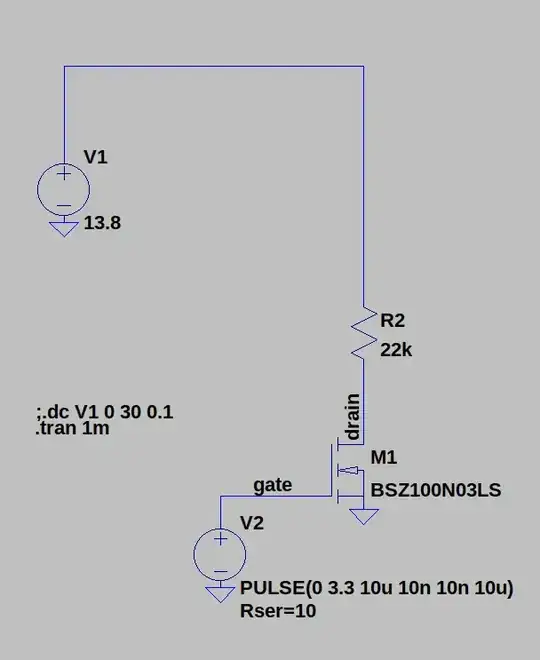

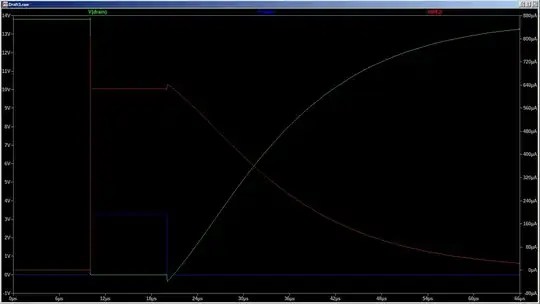

Hi folks, I'm simulating this very simple common source circuit with an NFET, with a pulse input on the gate input. On the falling edge of the gate voltage, I see a small negative output excursion on the drain terminal of the FET.

I'm wondering why this is occurring.

The green plot is the drain voltage, and you can clearly see the negative excursion right after the gate voltage goes down.