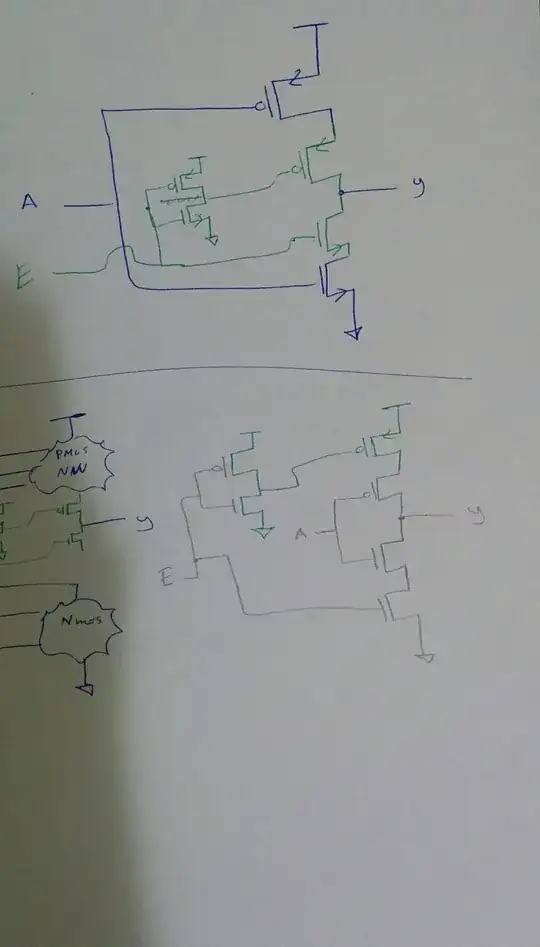

if we want to construct 3 state inverter...

Which case is better? Having the enable near o/p or far the o/p

I have seen people drawing it far the o/p. But can't figure out why

Do you see? The upper inverter has the enable near the output. The lower inverter has the enable far the output.

According to the professor, both works. But one of them is better (which one is faster ?)

( I did spend hours searching btw )

Asked

Active

Viewed 71 times

-1

KilGrave 09

- 1

- 2

1 Answers

0

The Enable transistors near the output (above) ensure that transitions on A are not coupled to the output. tri-state inverter will be 'better' at tri-stating. The output will be shielded from VDD/GND and the signal.

For the circuit at the bottom, a transient at A can be coupled through parasitic caps to the output.

-

the difference between them is in the response, one of them is faster in switching. so i modify the question to this " which one is faster ? " – KilGrave 09 Oct 31 '18 at 15:25

-

Both works fine but the on the left is used mostly why???..... if it is, then why is it not in your post? – jsotola Oct 24 '18 at 19:48