I watched Ben Eater video on Youtube giving an introduction to tri state logic (https://m.youtube.com/watch?v=faAjse109Q8&t=98s).

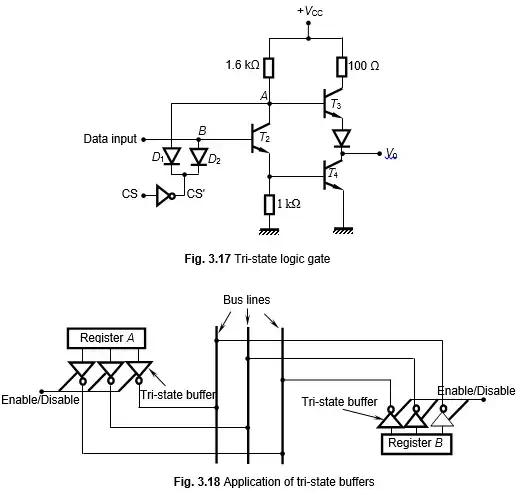

He first presents a circuit made of two transistors (see picture)

He shows that depending on whether the top or bottom transistor is on, the circuit will act as a current source or sink. Then he explains how this poses a problem with buses and the need of an enable pin.

He states that if both transistors are off, then the output is disconnected so it will not interfere with the bus. After that, he talks about using a specific chip for the job.

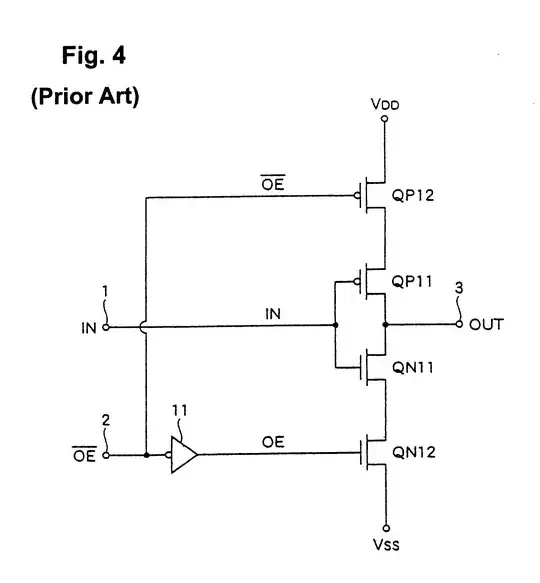

But I would like to understand how the enable pin actually works and how it can be implemented using low level electronic parts (transistors, resistors and the like).

How one effectively disconnect the output using a control signal? Does a simple transistor able to disconnect the output or is there more to tell about it?

I’m new to electronics so simple English answers will be appreciated.

Edit: if I plug the buffer input to the top transistor and plug the enable pin to the bottom transistor, will it do the job?