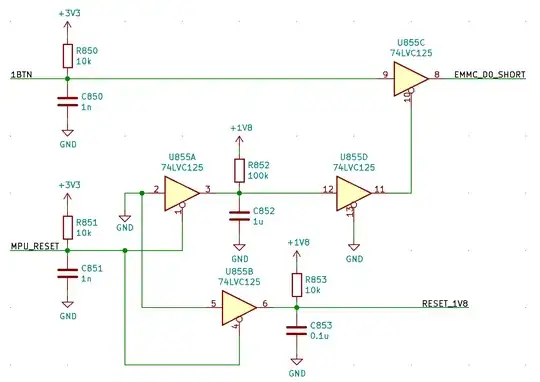

The attached image is a circuit using a rc-delayed (reset) signal to control a tristate gate (U855C).

After MPU_RESET is asserted, C852 starts charging. Gate U855D is always enabled. When the capacitor is chaged to roughly above 70% of Gate's VCC (1.8V), Gate D ouputs high and Gate C is disabled.

My question is, could I just connect RC to Gate C's OE_N pin directly, bypassing Gate D?

Theorectically, Gate C should be disabled when voltage at OE_N pin (pin 10) reaches about 30% of VCC (0.54V for 1.8V VCC), I can just tune the RC value to have a larger time constant.

Is there any pitfall to do this? The purpose is to save a gate for other usage.